AIを活用して半導体製造革新を目指すキオクシア/東芝/ローム/ソニー

間もなく開催されるISSCC2025のテーマは、「AI 革命を推進するシリコン エンジン」である。半導体技術がAIを推進し、そのAIがすべての製品やアプリで活用され(図1参照)、世の中を一変しようとしている。産業分野へのAI導入も例外ではなく、AIにより製造を効率化し生産性を向上させようという動きが欧米中心に進行している。日本の半導体メーカーでもそのような動きが顕著になってきた。

去る12月に東京で開催された国際半導体製造シンポジウムISSM2024でも、AIを活用して半導体製造を革新しようという発表が相次いだ(参考資料1)。「ノウハウをサイエンスに」を基本スタンスとするISSM2024で注目されたAIによる半導体製造革新に関する日本の半導体メーカー(キオクシア、東芝、ローム、ソニー)の発表を紹介して、日本の半導体製造現場でのAI活用の様子をレポートしよう。ほかにも興味ある発表が多数あったので、興味なる方は参考資料1を参照いただきたい。なお、 本文中にAI用語がいくつも出てくるが、わからない方はChatGPTのような生成AIに尋ねて理解を深めていただきたい。

図1 AIはすべての製品やアプリで活用されAI革命を起こす 出典:TSMC Mii上席副社長のIEDM 2024基調講演より

ベイズ最適化を用いて少ない実験回数でプロセス設計最適化 -キオクシア

キオクシアからは、「3D NAND フラッシュメモリのための多目的ベイズ最適化を用いたウェットエッチング設計最適化」 が発表された。ベイズ最適化とは、確率的推論に基づいて最適なパラメータや条件を探る、マシンラーニング(機械学習)の手法の一つである。

近年、半導体製造プロセスの複雑化に伴い、デバイス構造を高精度に最適化する必要性が高まっている。例えば、バッチ式のウェットエッチング装置では、プロセス槽内の薬液の流れの不均一性によりウェーハのエッチング状態にばらつきが生じることがある。この問題に対しては、実ウェ―ハを用いたエッチング実験の結果に基づいて装置構造を最適化することにより、さらに均一なエッチング状態を実現することができる。しかし、この方法では、多数の試行実験と専門的な知識が必要となり、非効率である。

3Dフラッシュメモリでは、ワード線形成時のSiNの選択的なエッチングにおいて、上述の問題が顕在化している。本研究では、多目的ベイズ最適化を利用した革新的な手法を導入し、エッチング液の流速、即ちエッチング液中のシリコン濃度を精密に制御可能な最適なウェットエッチング槽設計パラメータを導出した。この手法では、流体シミュレーションから得られた数値情報だけでなく、流体シミュレーション画像を用いてベイズ最適化を実施し、エッチング槽デザインを最適化している。その結果、実ウェ―ハ実験を行うことなく、短期間でエッチング槽デザインを最適化できるようになったという。

このように、キオクシアではプロセス条件を少ない実験回数で最適化するため、ベイズ最適化を活用しているが、ベイズ最適化での試行回数をさらに削減するため、同社は新たな初期実験計画法の発表も行った。この初期実験計画法では、複数の実験パラメータからなる高次元空間内に、少量の実験点を一様に配置する。

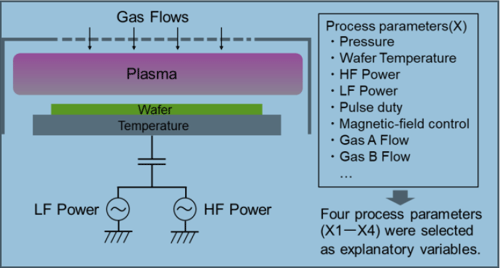

キオクシアは、300mmウェ―ハでの高アスペクトホール・ドライエッチングプロセスを例にこの手法の適用を具体的に示した(図2参照)。エッチング面内均一性に影響を与える可能性のある複数の実験パラメータを用いて、この初期実験計画法で導出した条件で初期実験を行った。さらにベイズ最適化で条件探索を行うことで、エッチング面内均一性が最適化されるまでの実験試行回数が、大幅に削減可能となることを示した。

図2 ベイズ最適化のためのドライエッチング装置におけるプロセスパラメータ抽出 出典:KIOXIA

ドメイン知識の転移学習による仮想計測 -東芝

東芝グループは、ドメイン知識の転移学習による仮想計測(VM)について発表した。領域知識の転移学習とは、ある問題を解決する際に得た専門的な知識を別の問題の解決に焦点を当てた機械学習(マシン・ラーニング)の一種である。

計測(VM)は半導体製造において、センサデータを用いてウェーハの特性を予測するために不可欠である。ただし、高次元性や非定常性などの問題により、正確な VM を構築することは困難である。Lasso (Least Absolute Shrinkage and Selection Operator)

などの従来の方法では、特徴選択とパラメータ推定を同時に実行するが、ドメイン知識と競合する可能性がある。そこで、東芝は、ドメイン知識を回帰モデルに組み込む新しい方法である Weighted Transfer Lasso を紹介した。反応性イオン エッチング データを使用した実験では、従来の方法と比較して精度と一貫性が向上していることが実証され、信頼性の高い VM 更新の可能性を東芝は強調した。

歩留まり低下要因解析にAIを活用 -ローム

ロームは、「大規模言語モデルを活用した迅速かつフレキシブルな歩留まり分析」について発表し、ISSM2024最優秀論文賞に輝いた。

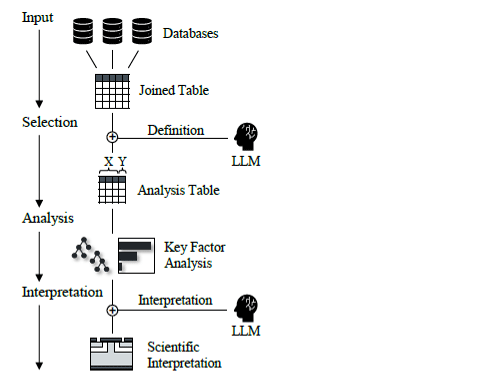

半導体製造には複雑な工程がたくさん含まれるため、経験豊富な技術者であっても製造歩留まり低下要因について解析することは困難である。ロームは、「あるパワー半導体製品の特性がある期間悪化した」というような場合について、特定の特性に影響を与える要因を特定するためのフレームワークを提案した。このフレームワークは、入力、選択、分析、解釈の4つのレイヤーで構成されており、選択と解釈のレイヤーにおいては、AIに基づき重要な革新がなされている。

選択レイヤーでは、大規模言語モデル(LLM)が分析表のメタデータを利用して列の属性を推測し、行のフィルタリングとターゲット変数の識別のための列の正確な決定を容易にしている。解釈層では、プロセス情報と相関を統合し、実行可能なプロセス改善やリスク評価を提案している。このアプローチは、歩留まり解析を改善し、生産データを効果的に解釈するために、LLMをドメイン固有の手法と統合する可能性を示唆している。ロームは、半導体製造プロセスにおける歩留まり改善努力を合理化し、コスト削減を図り生産性向上の可能性を強調している。

図3 歩留まり低下要因を特定するための選択・解釈段階でのLLM活用 出典:ROHM

ディープラーニングを用いたウェーハ表面欠陥検出の改善 -ソニー

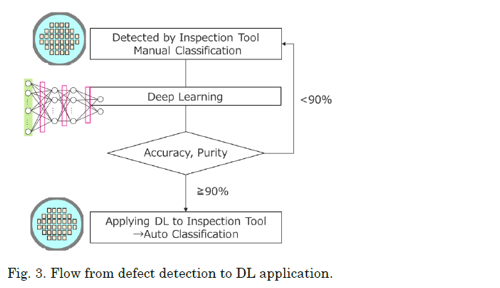

ソニーセミコンダクタからは、「ディープラーニングを用いたChip-on- Wafer (CoW)表面欠陥検出の正確さの改善」と題する発表が行われた。CoWプロセスの品質を確保するためには,高感度での表面欠陥検査が不可欠であるが,ダイシング・ソーティングされたチップ上の微小欠陥を高精度かつ効率的に検出することは,特定の偽欠陥の存在により,ウェーハ全体の欠陥検査よりも困難である.本研究では、ディープラーニングを用いた画像自動分類を適用することで、偽欠陥の検出率を低減し、目的の欠陥のみを検出することに90%以上の正確さで成功したという。

図4 Chip-on-Wafer上の欠陥検出へのディ−プラーニングの活用 出典:SONY

日本を世界一の半導体大国に押し上げた20世紀の日本のモノ造りは、熟練技術者や作業員のカンと経験に支えられてきた。それが今や欧米中心にAIに置き換わり、さらに正確な生産条件の最適化や製造の効率化を迅速に行えるようになって生産性が著しく向上してきており、日本勢もうかうかしてはいられない。日本の半導体メーカーは、さらにAIを活用して国際競争力をつけて再び世界へ飛躍することを期待したい。

参考資料

1. ISSM Website