貿易対立の強まりを受けて自国の半導体製造を強化する米中

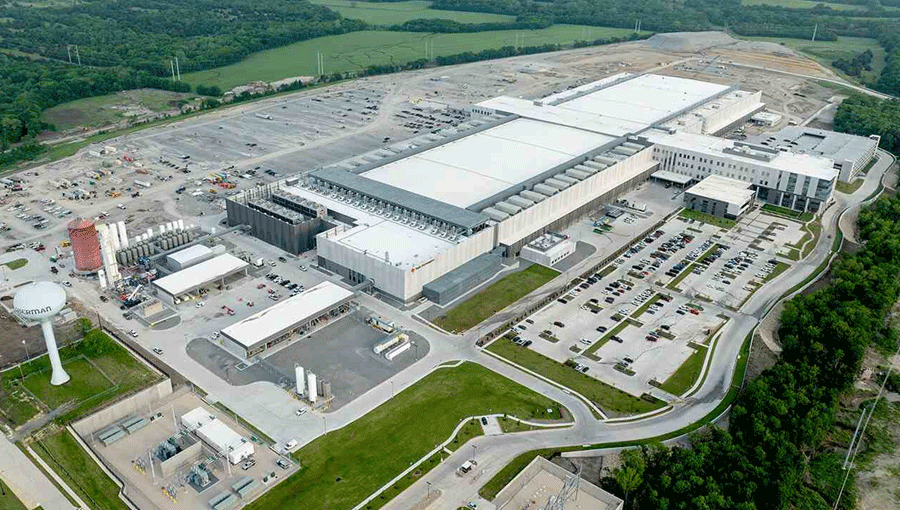

米中対立から、サプライチェーンをできる限り自国に持ってこようとする米中の動きが顕著になってきた。米アリゾナ州のTSMC工場は第2工場がすでに動き出し、第3工場への投資も出ているという。テキサス州でもIT各社による「スターゲート計画」と呼ぶAIデータセンターの街を作る計画がある。中国の自動車は国産半導体を100%に上げる方向にある。国内でもソニーが22nmのラインを動かし始める。 [→続きを読む]

米中対立から、サプライチェーンをできる限り自国に持ってこようとする米中の動きが顕著になってきた。米アリゾナ州のTSMC工場は第2工場がすでに動き出し、第3工場への投資も出ているという。テキサス州でもIT各社による「スターゲート計画」と呼ぶAIデータセンターの街を作る計画がある。中国の自動車は国産半導体を100%に上げる方向にある。国内でもソニーが22nmのラインを動かし始める。 [→続きを読む]

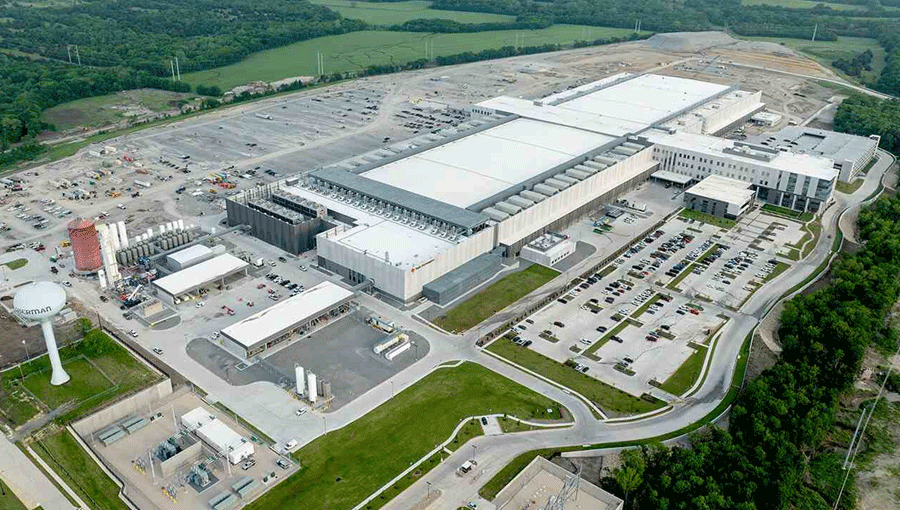

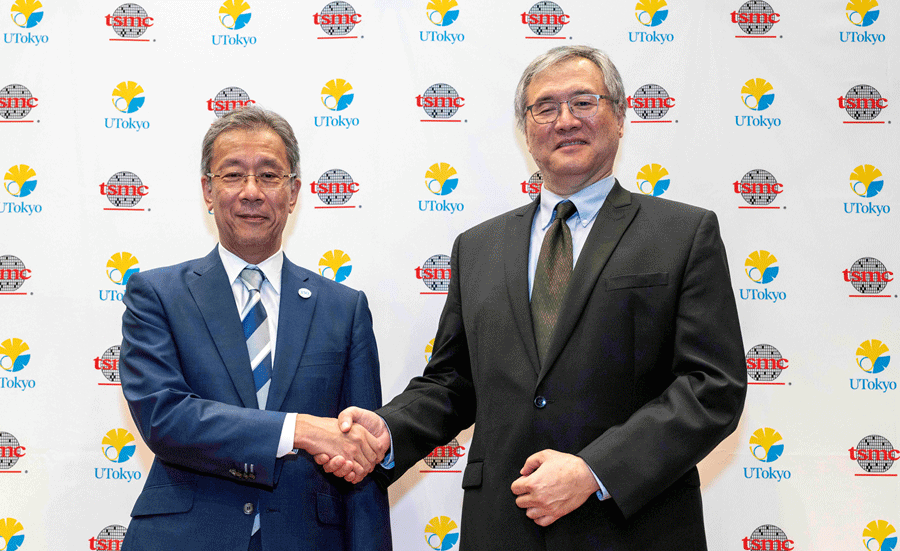

東京大学とTSMCが共同のラボを浅野キャンパスに設けると発表した。TSMCと台湾以外の大学との共同ラボは初めて。東大にはこれまで材料や半導体物理、電子回路などで豊富な研究者がおり、TSMCにとっては共同できることが1.4nm以下のプロセスノードとなると東大とのコラボは心強い。東大にとってもVDECを通してチップ試作を依頼してきた。今回の特長は何か。 [→続きを読む]

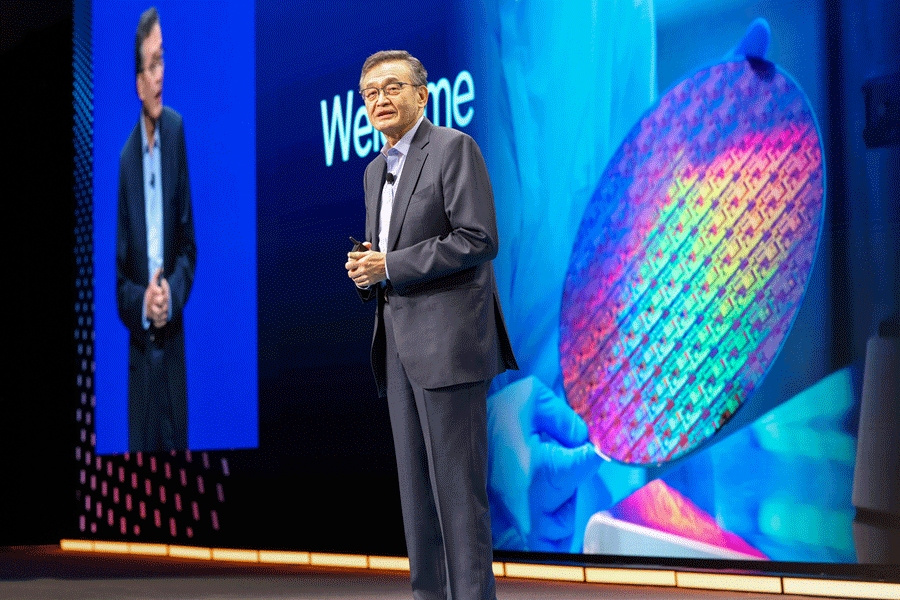

米Intelがファウンドリをビジネスとして確立するためのパートナーとのエコシステムを、新CEOであるLip-Bu Tan氏が、このほど開催したIntel Foundry Direct Connectで明らかにした。同氏はIntelを、技術、カスタマフォーカスだけではなく企業文化も変えることを訴えており、ファウンドリとしてのパートナーとして、EDAトップ3社に加え、PDF Solutionsを紹介した。 [→続きを読む]

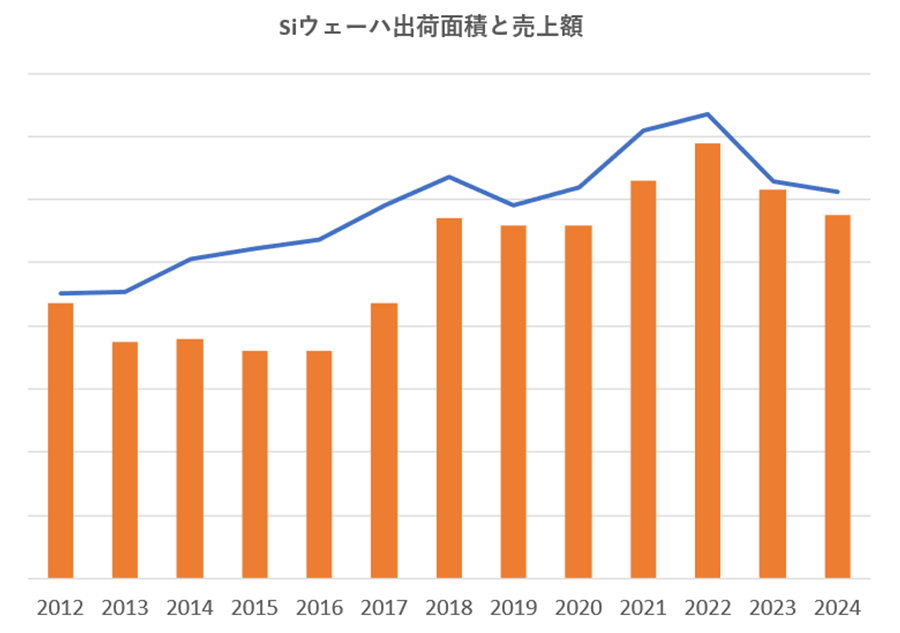

2024年におけるシリコン半導体ウェーハの出荷面積が前年比2.7%減の122億6600万平方インチだったとSEMIが発表した。その年のウェーハ売上額は同6.5%減の115億ドルだった。出荷面積の減少よりも出荷売上額の減少の方が大きいということは、在庫調整がゆっくりで、ファブの稼働率を上げるような大量生産品目のデバイス需要が弱かったことを意味する。 [→続きを読む]

JEITA(電子情報技術産業協会)が12月19日に発表した世界の電子機器とソフトウエアやソリューションを合わせた電子情報産業の市場は、2025年に前年比8%増の3兆9909億ドルになる。TSMCの熊本工場が稼働し始めているが、九州に続々半導体プロセスに使う装置や材料の企業が続々集まっている。ラピダスにEUV装置が入り始め、関連企業もEUVに備えている。キオクシアは18日、東京証券取引所の東証プライム市場に上場した。 [→続きを読む]

産業技術総合研究所がEUVリソグラフィを導入して5nm以下のプロセス開発を支援する、と22日の日本経済新聞が報じた。これはIntelとの共同で整備する先端半導体の研究開発拠点に導入する。1000億円を投じるという。一方、日本にファウンドリ工場を新設するとしていた台湾のPSMCがSBIとの提携解消について理由を述べている。また、QualcommとArmとの係争が激化している。 [→続きを読む]

メーカーとサプライヤとの関係がひっくり返る事例がNvidiaとTSMCとの間に見られる。これまではファブレス半導体としてのNvidiaが設計したチップをTSMCが製造するという関係だった。今度はTSMCがメーカーとなり、プロセス中によく使うリソグラフィ工程でより正確なマスクを作製するための計算に、サプライヤであるNvidiaのGPUを利用するのだ。 [→続きを読む]

IEDM(International Electron Devices Meeting)2024の内容が明らかになった。70周年を迎える今年は、「明日の半導体技術を形作る」という全体テーマで、基調講演、一般講演だけではなく、フォーカスセッションやチュートリアル、ショートコースなど270件の講演が予定されている。例年通り米サンフランシスコのヒルトンホテルで12月7日から開催される(図1)。 [→続きを読む]

産業技術総合研究所は、ペロブスカイト構造の太陽電池の実用化に向け、自動作製システムを試作した。ペロブスカイト太陽電池は、変換効率がシリコン以上の高い効率を示す試作は多いが、バラつきが大きいと共に、経時変化が大きく劣化しやすい、大面積が難しいなどの問題が山積み。少しでも手作業による作製ではなく自動機によってバラツキを減らす狙いで装置を開発した(図1)。 [→続きを読む]

リソグラフィ最大手ASMLはIntelのオレゴン工場にHigh-NA(Numerical Aperture:開口数)のEUV装置を初出荷したが、海外複数のメディアによると、早くも次のHyper-NAのEUV装置開発が始まりそうだ。従来のEUV装置のNAは0.33でHigh-NA装置は0.55、そしてこれから開発するHyper-NAは0.75となり、これまで以上に微細加工が可能になる。 [→続きを読む]