2025年12月18日

|技術分析(プロセス)

佐賀大学の嘉数誠教授らのグループは、ダイヤモンド結晶を使って半導体としてMOSトランジスタを試作し、その高周波特性を測定したところ、遮断周波数fMAXが120GHzを示した。ダイヤモンドはバンドギャップがシリコンの4.9倍もあり耐圧が高いため、パワー半導体への応用が期待されている。とはいえ、実際のトランジスタを形成することは簡単ではない。ゲート絶縁膜、n型/p型の形成などシリコンとは難しさが違う。

[→続きを読む]

2025年12月 9日

|技術分析(半導体応用)

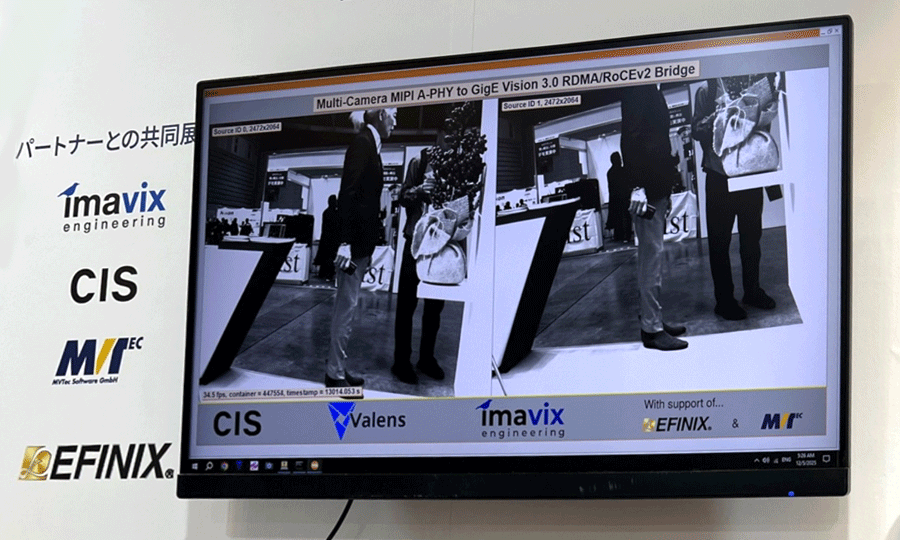

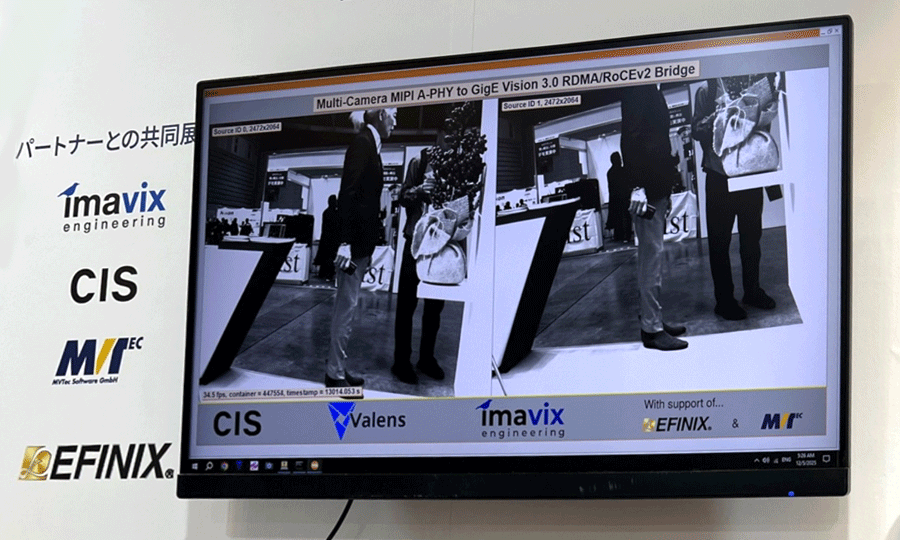

電磁波ノイズに強いSerDesチップを売りにしているValensは、自動車メーカーへの売り込みに成功した後、産業向けにも進出してきた。産業向けは独自仕様が多く、1社だけではシステムを設計・製造できないため、エコシステムの構築に力を注ぎ、顧客に提案できるまでになった。低消費電力、高性能、低コストのFPGAメーカーEfinixも参照ボード設計に加わった。

[→続きを読む]

2025年11月28日

|技術分析(プロセス)

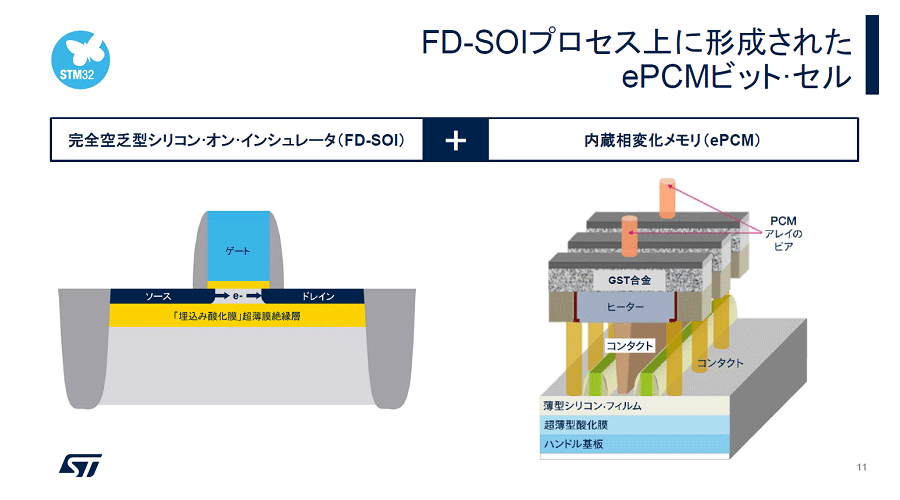

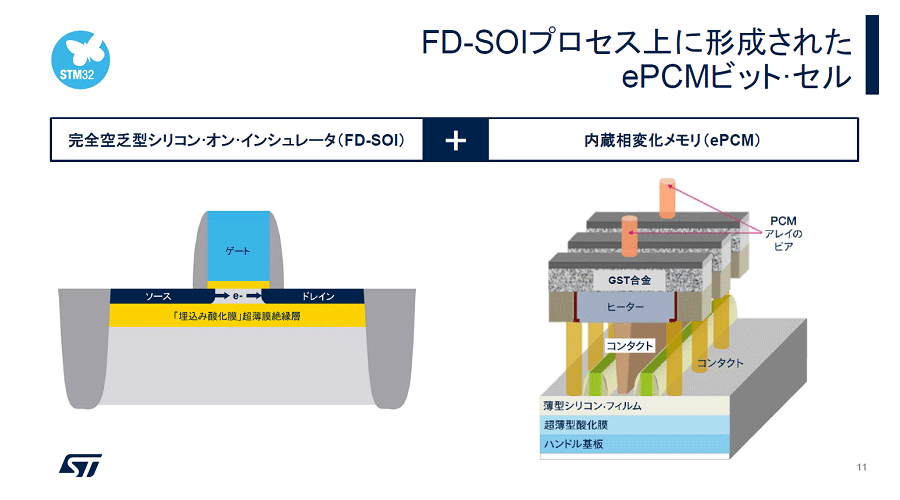

STMicroelectronicsは、初めてマイコンに18nmノードをもたらした。新製品STM32V8は、FD-SOI(完全空乏化シリコンオンインシュレータ)プロセスにPCM(相変化メモリ)を使い微細化を果たした。これまでのマイコンでは、NORフラッシュメモリを使っていたが、微細化が難しく40nmプロセスでほぼ止まっていた。28nm製品はあるが、ぎりぎりだった。実は、ストレージ部分をNORフラッシュから新型メモリに変えることでマイコンの性能は一段と上がることになる。

[→続きを読む]

2025年11月27日

|技術分析(半導体製品)

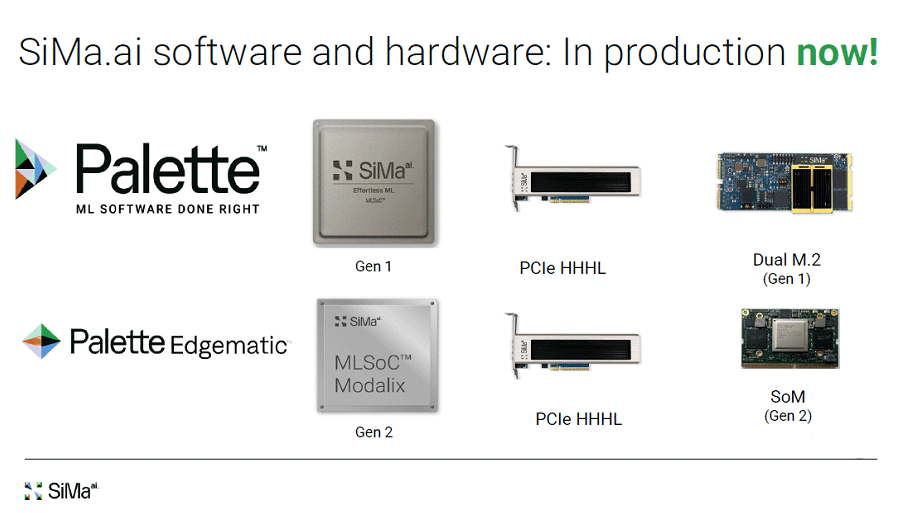

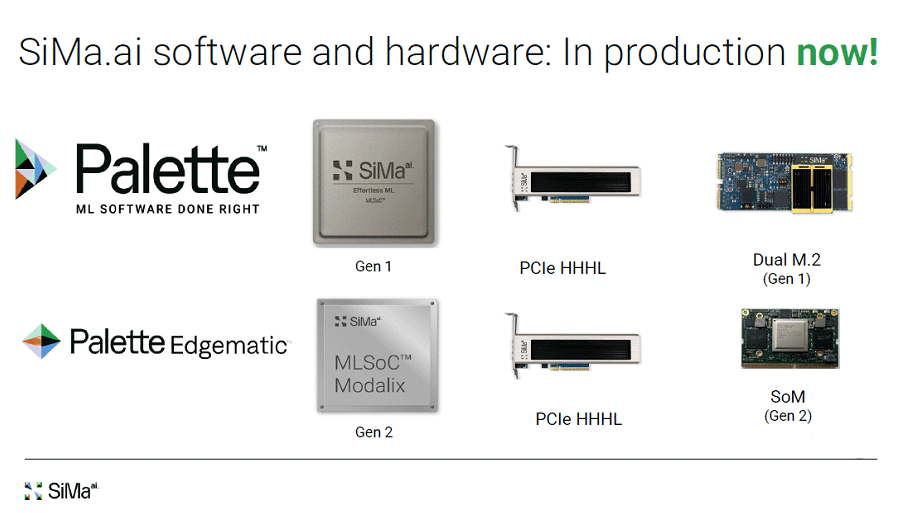

人が話しかければ、言葉で答えてくれる。しかもインターネットにつなぐ必要もない。こんなエッジAIを実現するAIチップをスタートアップのSiMa.ai(シーマドットエイアイ)が開発した。LLM(大規模言語モデル)を使って受け答えだけではなく、映像データも分析する。4000FPS(フレーム/秒)という超高速度映像にも対応する。エッジAIだからこそクルマやドローン、ロボット、監視カメラなどでの広い応用が期待される。

[→続きを読む]

2025年11月14日

|技術分析(製造・検査装置)

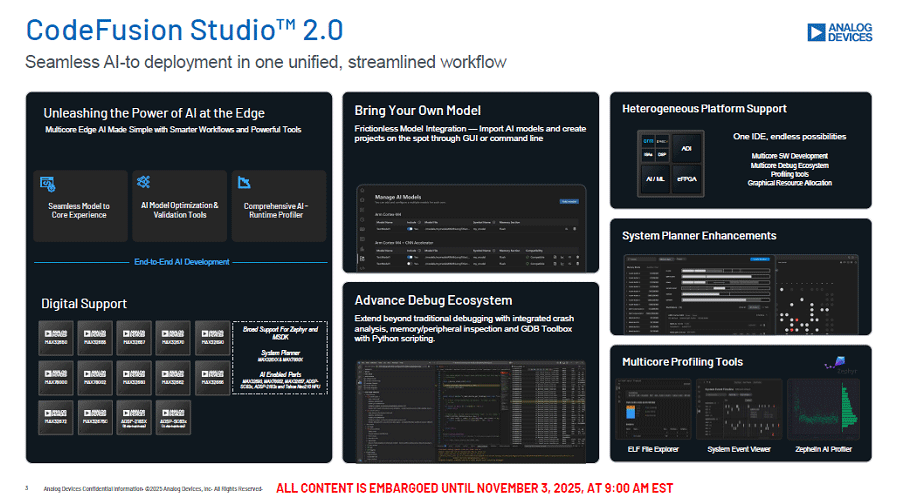

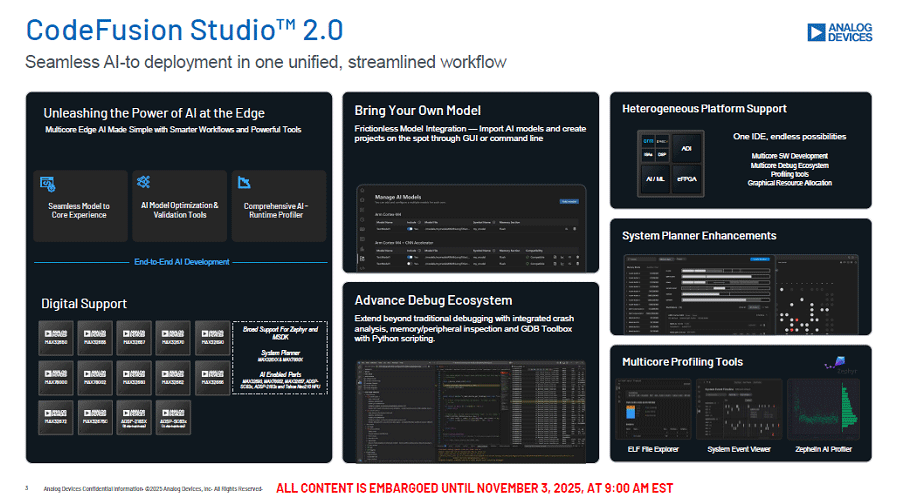

Analog Devices(ADI)は、これまでの組込系開発環境であるCodeFusion Studio 1.0にAIワークフローをサポートする機能を盛り込んだCodeFusion Studio 2.0をリリースした。これは、AIモデルをシームレスにインポートし、GUIやコマンドを通してプロジェクトを生成できるツールだという。AIモデルを取り込める統合開発環境といえそうだ。

[→続きを読む]

2025年11月 5日

|技術分析(半導体製品)

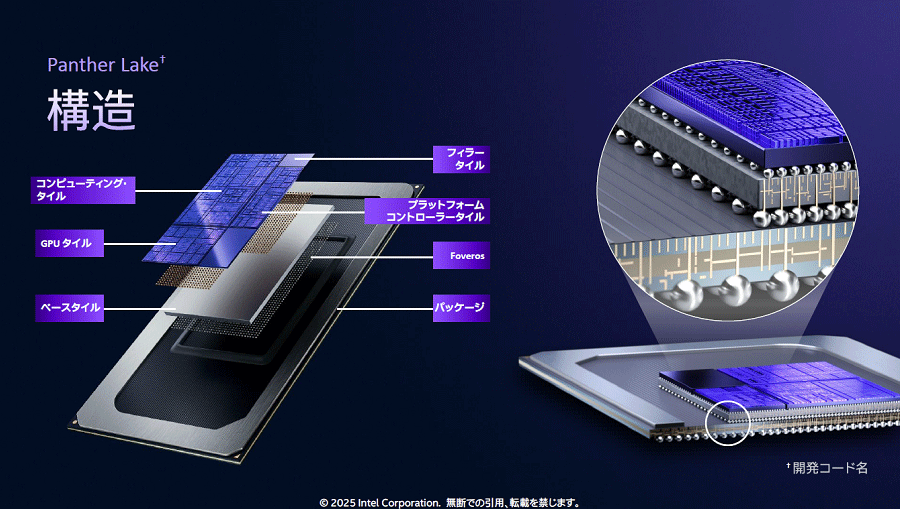

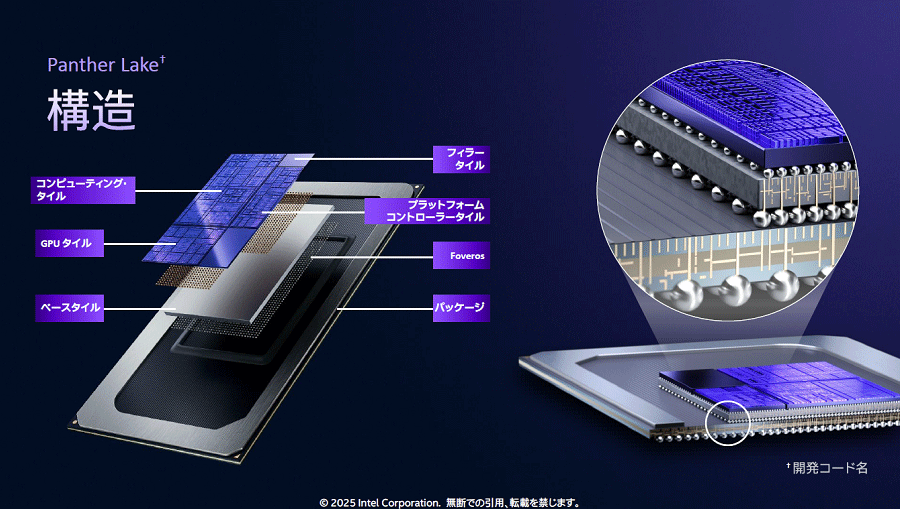

Intelはパソコン向けにIntel 18Aプロセスを使ったSoC「Panther Lake」を発表していたが、このほどその詳細を明らかにした(図1)。最近のCPUはCPUだけではなくGPU(グラフィックプロセッサ)やNPU(ニューラルプロセッサ)などを集積しており、CPUと呼ぶにはふさわしくないため、SoCと呼ぶ。Panther Lakeは3種類の製品シリーズがあるが、全て同じパッケージ、同じピン配置を採っている。

[→続きを読む]

2025年10月30日

|技術分析(プロセス)

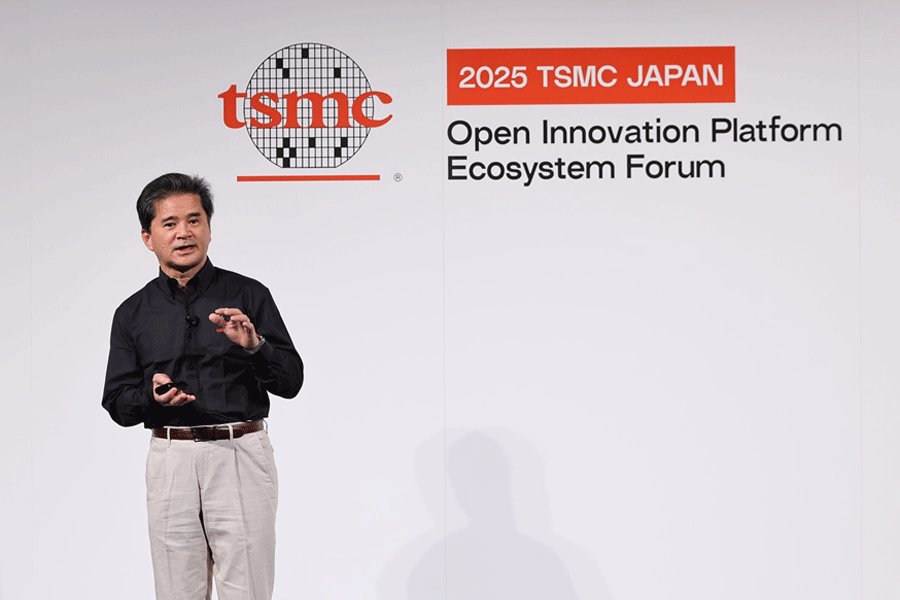

TSMCが東京でTSMC 2025 Japan OIP(Open Innovation Platform)Ecosystem Forumを開催、この3年間AIによってOIPは成長した、とTSMCジャパンの小野寺誠社長(図1)が述べた。AIがあらゆるデバイスに入り新しい応用を生む時代に入ったことを印象付けた。AI時代ではコンピュータ能力をもっと欲しいという要求が高まり、さらに高集積になるSoC設計が難しくなってきた。

[→続きを読む]

2025年10月15日

|技術分析(半導体製品)

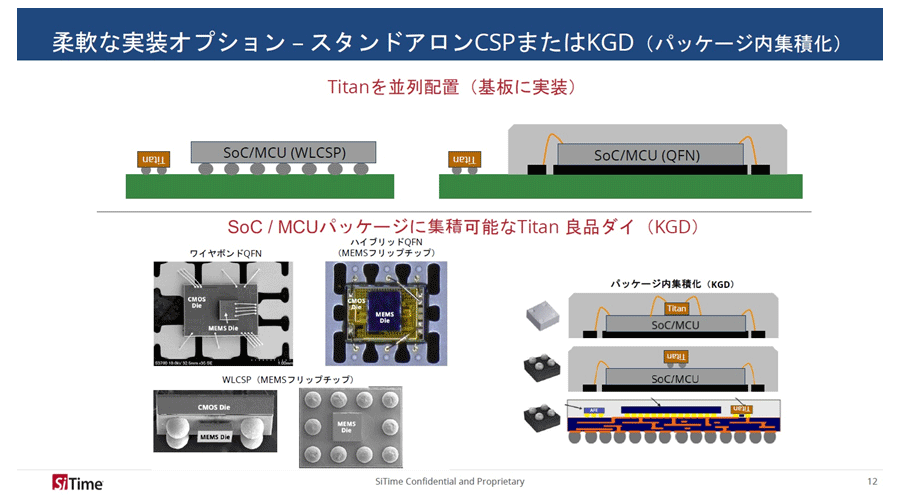

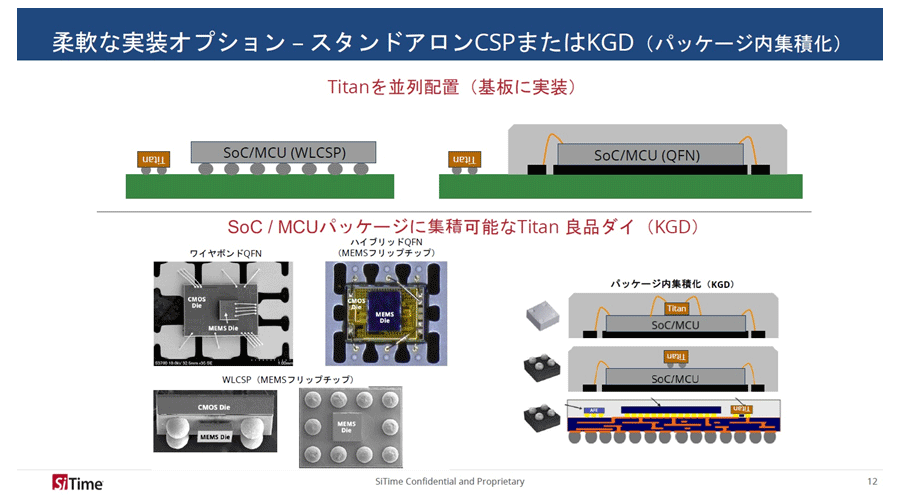

電源と同様、デジタル回路では水晶振動子のような安定な振動子は欠かせない。しかし、MEMS振動子が水晶振動子を超えただけではなく(参考資料1)、超小型のMEMS振動子Titanを開発したSiTimeは、新市場を手に入れつつある。従来の水晶振動子で最も小さい製品の1/4しかないTitanは、SiPパッケージ内にも導入できるレベルにやってきた。

[→続きを読む]

2025年9月24日

|技術分析(製造・検査装置)

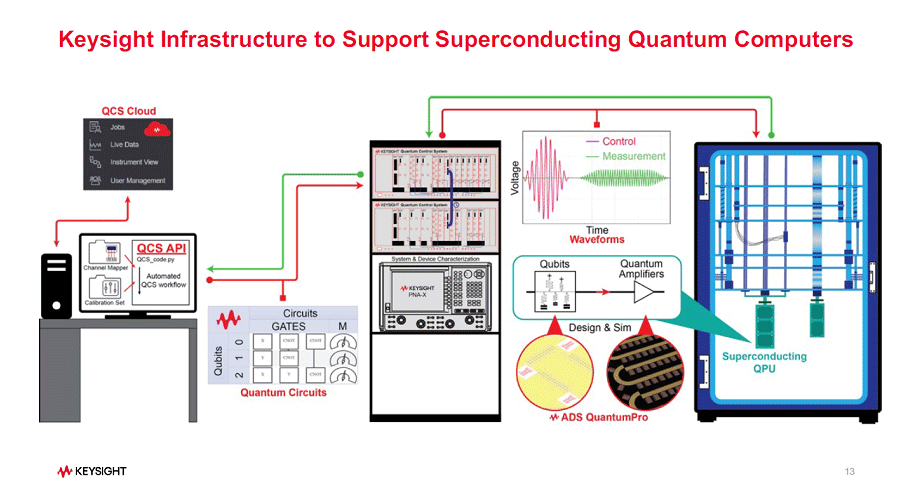

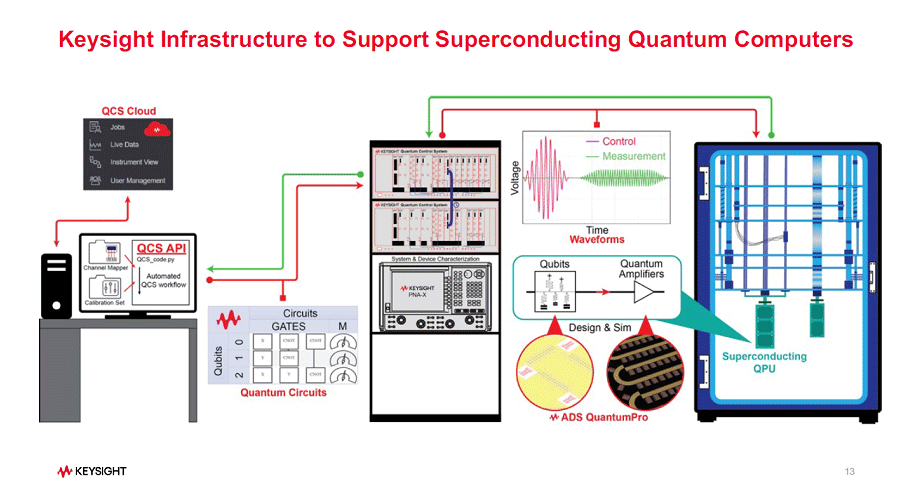

測定器メーカーのKeysight Technologiesが毎年恒例のKeysight Worldを開催、今年は任意波形発生器やハイエンドオシロスコープなどを駆使する量子コンピュータの測定システムQCSも示した(図1)。1000Qbitsまで対応できるシステムだと誇示した。キモはどうやらノイズの影響をいかに下げるか、のようだ。量子状態の実現は熱振動を避ける所から始まる。

[→続きを読む]

2025年9月12日

|技術分析(半導体製品)

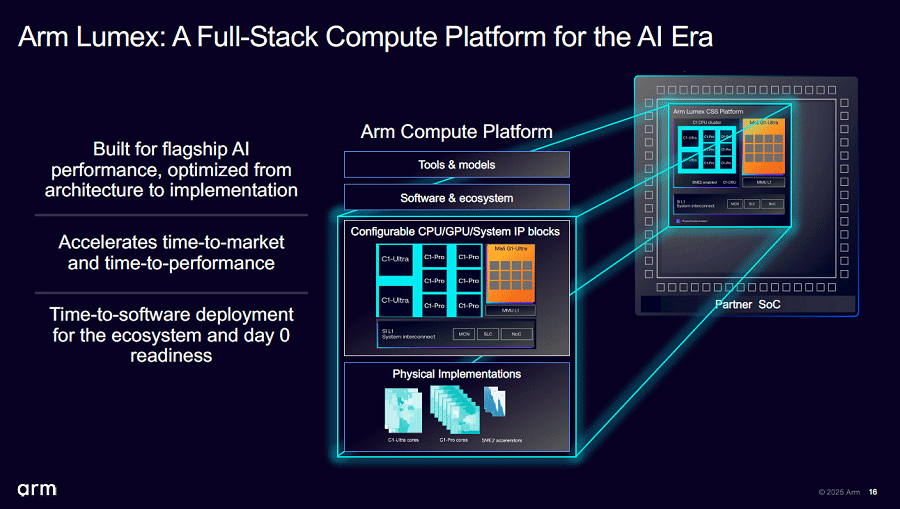

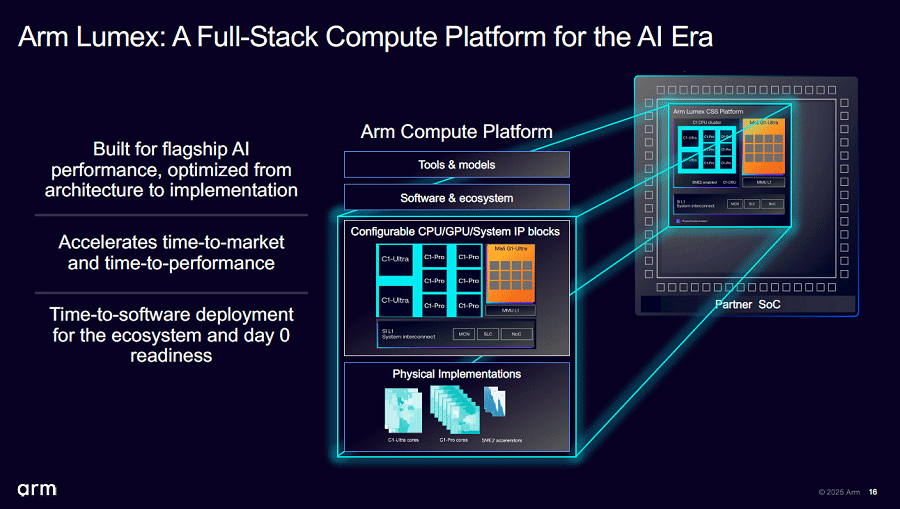

IPベンダーのArmは、モバイルAI向けにCPUとGPUとAIアクセラレータを集積できる巨大なIP「arm lumex」を提供すると発表した。同社はこれをCSS(Compute Sub-Systems)プラットフォームのモバイル版と呼び、データセンター向けの「Arm Neoverse」、車載向けの「Arm Zena」に続く、シリーズの一つである。スマートフォンにも巨大なIPでAIワークロードを実行することになる。

[→続きを読む]