Xilinx、超高級2.5D-LSIの全貌を明らかに

Xilinxは、高度なLSIは全てFPGAで組むのではなく、ソフトウエアベースのマルチコアCPUや、ダイナミックに再構成可能なハードウエアエンジン、AI専用推論回路、DSP、DDR RAM、周辺回路、I/Oなどを集積する「超高級LSI」ACAP(Adaptive Compute Acceleration Platform:適応型演算加速プラットフォーム)の狙いを明らかにした。

図1 Xilinx社CEOのVictor Peng氏

これは、実装形態上はシリコンインターポーザを用いた2.5次元LSIそのものであるが、これからの大規模LSIの方向として、CPUとDSP、AIエンジン、そしてFPGAを集積することでほとんど全ての機能を実現できるようになる。汎用でありながらプログラム可能な高速エンジンとなる。この高級な半導体を開発したのは、もはやFPGAの会社ではなく、データ爆発に対応できる会社を指向するためだ、と今年のはじめにCEOに就任したVictor Peng氏(図1)は述べた。

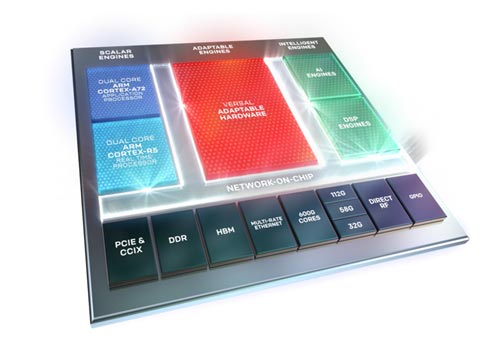

提案されたACAPに集積される回路ブロック(図2)を紹介しよう。大きなブロックは4つある。一つはスカラー処理エンジンと呼ぶ、いわゆるCPUである。ここにはArm Cortex-A72アプリケーションプロセッサと、Arm Cortex-R5リアルタイムコントローラを搭載している。いわばソフトウエアプログラミングでカスタマイズする、やや高級なCPUである。このLSI全体を制御する回路がCortex-R5である。

図2 Xilinxが提案した2.5D-ICのACAP 出典:Xilinx

そして、VARSALと呼ぶ適用型ハードウエアエンジンは、専用の演算回路を作るためのハードウエア回路である。ここはFPGAを基本とする専用IP回路であるが、最大3個の専用回路を予めFPGAで構成しておき、動作中にその専用回路を切り替えることでダイナミックな再構成回路を実現するという訳だ。このIPは、小さな機械学習のアプリケーションや再利用可能なロジックなどをタイムシェアリングのように順次切り替えていく。場面に応じてアダプティブに切り替えればよいため、アダプティブ(適応型)ハードウエアエンジンと呼んでいる。ちなみにVARSALという呼び名は、多様性を意味するVersatileと汎用性を意味するUniversalを合わせた造語である。

三つ目がDSP(デジタル信号処理)エンジンである。DSPは、積和演算専用のマイクロプロセッサだが、高度なモデルを数値演算するのに使うことが多い。通信基地局のモデムのアルゴリズムを計算したり、自分専用に打ち立てたモデルを計算したりするため、32ビット(単精度)ないし64ビット(倍精度)のように精度の高い浮動小数点演算が可能であるだけではなく、カスタマイズされたデータパスを低いレイテンシで粒度の細かい制御が可能だとしている。

四つ目が推論専用のAIエンジンである。AIの推論と高度な信号処理に向いた、高スループットで低レイテンシ、高い電力効率を特長としている。Xilinxはディープラーニングの推論プラットフォームを手掛けている中国Deephi社を今年の7月に買収しており、Xilinxは買収以前からこのスタートアップ(2016年設立)に出資していた。しかもDeephiは推論アクセラレータをFPGAで実装していたので、新しいACAPにも自然に取り込むことができた。CaffeやTensorFlowなどのフレームワークで学習したデータをこのAIエンジンでコンパイルしてSoCに実装できる。

AIエンジンは、並列処理する場合にはSIMD(Single Instruction Multiple Data)命令で行列演算を行い、VLIW命令でスケジューリング制御する。AIエンジン内の各種ベクトルプロセッサコアはメモリとセットになっており(図3)、機械学習ではこの小さなベクトルプロセッサとメモリの対の回路で構成され、超並列で演算していく。

図3 集積したAIエンジンのIPコア 出典:Xilinx

周辺回路として、インタフェースではPCIeのGen4×16や、AXI-DMAなどを搭載している。メモリとしてはDDR4-3200やLPDDR4-4266などのDRAMや、DRAMアレイチップを3次元ICとして接続されたHBM(High Bandwidth Memory)を搭載できる。さらに100Gbpsのマルチレートのイーサネットや暗号化エンジンも搭載できる。もちろん、32Gbpsないし58Gbpsの高速インタフェースPAM4も用意する。最高速の112Gbpsも用意するがこれは7nmプロセスで実現する予定となっている。

さらに、今後の5Gワイヤレス通信向けのモデムや次世代GPS向けのRF-ADC/DAC、デジタルアップコンバータとダウンコンバータも内蔵したRFシグナルチェーンIPも準備する。そして、各回路ブロックをつなぐ配線はバス方式ではなく、スイッチで切り替えるようなNoC(Network on Chip)方式を取る。このNoCのIPは独自に開発したもの。単なるリピータを含むのではなく、ヘテロなエンジン全体のアービトレーション(データ競合を整理する仕組み)が可能な構造になっている。

最小寸法7nmプロセスで製造するこのACAPは、最高級の回路を集積しており、顧客の要求に応じて回路を切り分け、さらに再利用できるフォーマットを取る。