セミコンジャパン2023、先端パッケージング技術が続出(1)

セミコンジャパン2023では、OSATのアオイ電子、前工程の製造装置のTEL、ウシオとAMATの提携、良品チップを積層した後のテストを探るアドバンテストなど、2.5Dや3DのICやチップレットを実装する先端パッケージング技術が続出した。2.5D/3D-ICやチップレットなどを多用して集積度を各段に上げることができる。先端パッケージングの装置メーカーが続出した。1部と2部に分けて掲載する。

図1 久しぶりにセミコンジャパンは賑わった 東京ビッグサイトの東1〜6ホール全部と新しい東7と東8ホールを占めた

12月13日〜15日、東京ビッグサイトで開催されたセミコンジャパン2023(図1)は、コロナ以前よりも賑わった。半導体産業の重要性が見直され、学生や若い女性が半導体製造装置のブースで身を乗り出して話を聞く姿があちらこちらで見受けられた。2022年に5万1480名だった来場者は、今年は8万5282名と跳ね上がった。ブースは東京ビッグサイトの東1〜6ホールまでの全館と新しいホール7と8を占めた。

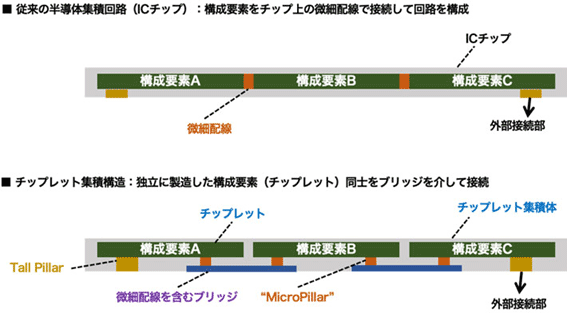

セミコンジャパン2023では先端パッケージング技術が注目された。東京工業大学特任教授の栗田洋一郎氏は、チップレットやチップ(ダイ)との間をシリコンインターポーザではなく、もっと小さなブリッジチップで接続する技術をアオイ電子のブースで見せていた。これは、再配線層を形成しているブリッジチップと、チップレットやチップをCu(銅)のマイクロピラーで接続しようというもの(図2)。IntelのEMIB(Embedded Multi-die Interconnect Bridge)技術と似ているが、EMIBではブリッジチップをプリント回路基板に埋め込んでおく必要がある。これに対して、栗田教授の方法は、チップレットやチップ間をブリッジチップで先にマイクロCuピラーを用いて接続し、その後でチップレットやチップは基板と接続する。EMIBよりも簡単な工程になる。

図2 東京工業大学の栗田洋一郎教授が開発したパッケージング技術 出典:東京工業大学

先端パッケージは配線幅が現在最先端の50µm程度から10µm以下の加工が求められる。栗田教授のマイクロピラーやブリッジチップ内の再配線層の形成などにはこれまでの配線幅とは桁が違う微細加工技術が必要になる。

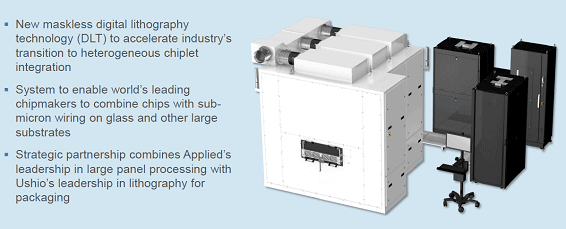

Applied Materialsとウシオが提携して少量多品種用のリソグラフィ装置を開発している。デジタルリソグラフィと呼ぶその装置は、マスクレスで配線パターンをインターポーザやガラスなどの回路基板(サブストレート)に直接描く。このリソグラフィ技術では配線幅2µm以下の配線パターンに対応できる。これまでのプリント回路基板向けのリソグラフィは10µm以上の配線パターンだったため、半導体ウェーハ向けのサブミクロンのリソグラフィ装置では対応できなかった。プリント回路とシリコンウェーハとの間を埋めるリソグラフィ装置が今回のDLT(Digital Lithography Technology)装置である。

図3 Applied Materialsとウシオが共同開発したDLTリソグラフィ装置 出典:Applied Materials

なぜこの装置開発が必要だったか。要求が強いのは生成AIである。巨大なソフトウエアの生成AIを学習させるのに長い時間がかかっていた。チャットGPTの学習には300日もかかったと言われている。このため大半のAIソフトウエア技術者はコードが長すぎるため、ソフト開発をほぼあきらめていた。学習に必要なGPUの性能が不足していたからだ。巨大なソフトには巨大な半導体チップで対抗するしかない。しかし、レチクルサイズでチップサイズは決まってしまう。しかも大きなサイズのチップは歩留まりが落ちてしまう。

そこでチップ内の小さな集積回路やIPをチップレットという形で切り出して、さまざまなプロセッサのチップ(ダイともいう)を平面に搭載したり3次元的に重ねたりしてヘテロ集積回路を構成する、先端パッケージ技術が登場した。この基板(サブストレート)に数µm幅の配線を描くのがAppliedとウシオが開発したDLTである。チップサイズとは無関係な集積回路を作れるため、生成AIのような大きなチップも楽に作ることができる。しかも生成AI向けのICだと、メモリやCPUほどの生産量は必要ないため、マスクレスでの生産が可能だ。また、ステッパと違い、レチクル境界でのパターンの歪みがない。

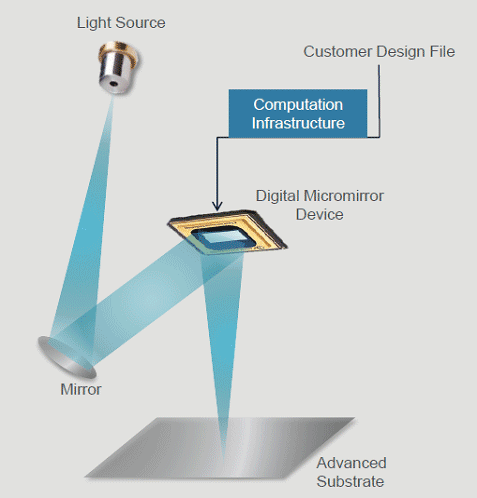

なぜデジタルリソグラフィと呼ぶのか。そのカギは、リソグラフィシステムに、デジタルミラーデバイス(DMD)を使っているからだ(図4)。DMDは48万〜800万個のMEMS技術のミラー(鏡)をマトリクス上に並べたデバイスである。Texas Instrumentsが開発した技術で、一般の映画館でプロジェクタとして使われている。回路の配線パターンはDMDを駆動することで描かれる。顧客の回路設計ファイルを入力することでパターンを描く。

図4 DLTの動作原理はDMDデバイスを使ってパターンを描く 出典:Applied Materials

ウシオはこれまでプリント回路基板向けのステッパを4000台以上出荷してきたという実績がある。しかし今回のようなレーザー直描装置は初めてで、Applied と共同で開発にこぎつけた。Applied はこの技術開発に責任を持ち、ウシオはリソグラフィ装置を販売する。すでに複数のカスタマに出荷して評価を受けていると段階だという。今回の製品は2µm線幅を対象としているが、次は1µmのリソグラフィシステム開発というロードマップも持っている。

(第2部へ続く)