TSMC、Siフォトニクス、ウェーハスケール集積回路の選択肢を提案

AIコンピューティングパワーがけん引し、プロセスノードの微細化は早まっている、とTSMCシニアバイスプレジデント兼副共同最高業務執行責任者のKevin Zhang氏が述べた。これは6月28日に横浜でTSMC Technology Symposium Japanを開催した際、メディア向け技術説明会で述べたもの。 [→続きを読む]

» セミコンポータルによる分析 » 技術分析 » 技術分析(プロセス)

AIコンピューティングパワーがけん引し、プロセスノードの微細化は早まっている、とTSMCシニアバイスプレジデント兼副共同最高業務執行責任者のKevin Zhang氏が述べた。これは6月28日に横浜でTSMC Technology Symposium Japanを開催した際、メディア向け技術説明会で述べたもの。 [→続きを読む]

2nmプロセスでは、EUVといえどもOPC(光学的近接効果修正)が必要になってくる。EUVの13.5nmという波長ではパターンをそのまま加工できなくなってきたからだ。2nmプロセスだと複雑すぎて試行錯誤的なアプローチはもはや使えない。計算機利用のリソグラフィの出番となる。NvidiaとTSMC、Synopsys、ASMLは、昨年エコシステムを構築したが(参考資料1)、TSMCの量産ラインに計算機リソを導入していることが明らかになった。 [→続きを読む]

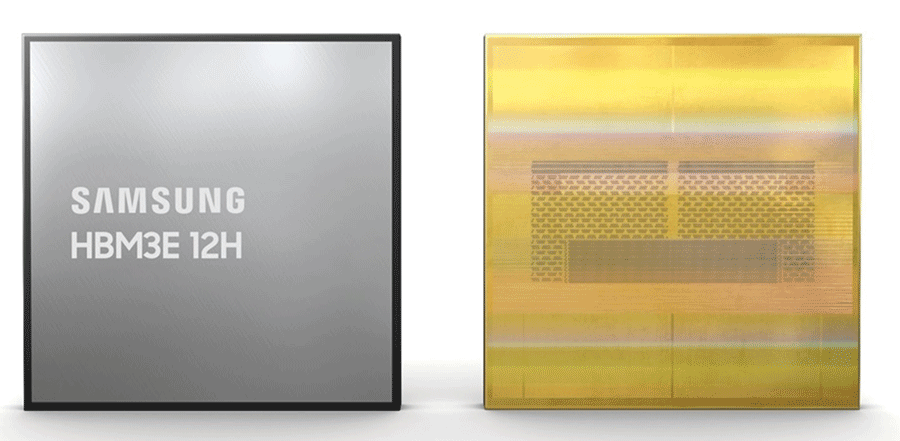

Micron、Samsungが3D-IC技術を使ったDRAMメモリであるHBM3Eを相次いで製品化した(図1)。HBMメモリは大容量のメモリを一度に大量に並列読み出しできるデバイスであり、AIチップやSoCプロセッサと一緒に使われる。SK hynixがこれまでHBM1や2、3のメモリ製品に力を入れてきたが、コストがかかるため他社はあまり力を入れてこなかった。 [→続きを読む]

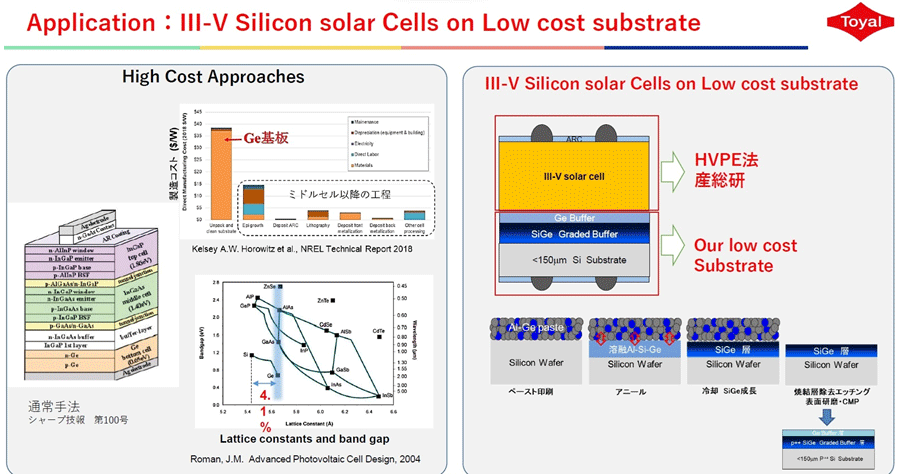

Si基板上にGe層を短時間で安価に作製する方法を東洋アルミニウムが開発した。Ge層の厚さを自由に変えられるだけではなく、ストイキオメトリ(化学組成)も制御できる。今のところ高価なGaAs系半導体向けの基板としての道を提案している。安価な太陽電池やSiフォトニクス、スピントロニクスなどの基板材料への応用を狙っている。 [→続きを読む]

フラッシュメモリの国際会議であるFlash Memory Summit 2023において、Most Innovative Flash Memory startup部門で最優秀賞を英国のスタートアップQuinas Technologyが受賞した(図1)。この新型メモリは量子力学的な井戸型ポテンシャルの共鳴トンネル現象を利用して電荷を出し入れする方式のデバイス。Quinasは英ランカスター大学の発明を事業化する企業。 [→続きを読む]

TSMCは自動車向けの半導体チップに関してもADAS(先進ドライバー支援システム)や自動運転向けなどの演算主体のSoCプロセッサ向けに、そして最先端の3nmプロセスノードの技術「N3AE」を自動車およびHPC(High Performance Computing)向けに、2024年に提供する。さらに高周波無線技術でも6nmノードを導入する。同社ビジネス開発担当シニアVPのKevin Zhang氏(図1)が語った。 [→続きを読む]

波長13.5nmのEUV(Extreme Ultra Violet)リソグラフィでもダブルパターニングが導入され始めた。ただし、解像度が30nmまでしか得られないため、位置合わせが難しい。Applied Materialsは、最小のパターン幅を安定に形成するパターンシェイピング技術を導入する装置「Centura Sculpta」を開発した。これを使えばダブルパターニングと同等な寸法を安定に形成できる。 [→続きを読む]

プロセスノード2nm以降の次世代半導体チップ製造に欠かせない、計算機リソグラフィ(Computational Lithography)のエコシステムをTSMCとNvidia、ASML、Synopsysが設立した。3nmノードの実チップ上での最小寸法が13nm台までやってきて、波長13.5nmのEUVリソでもOPC(光近接効果補正)の導入が欠かせなくなってきた。計算機リソはそのための技術である。 [→続きを読む]

プリント基板だけではなく、テフロンなどの基板にも密着性の良い配線を形成できる技術を岩手大学が開発、高周波特性の優れた回路を容易に形成できるようになる。岩手大のi-SBと呼ばれる技術は、分子接合材を用いる異種材料接合技術である。産業界もすでに着目し始め、実用化に向けたエコシステムの構築中だ。この技術を普及させるためのプラットフォームを今秋には構築する計画で進めている。 [→続きを読む]

半導体工場の脱炭素化が求められるようになってきたが、ベルギーの研究開発会社であるimecは、リソグラフィとエッチング工程における環境負荷を定量的に評価するシミュレーションを発表した。半導体プロセスの環境評価によりCO2削減への対策を打つことができる。まずはリソとエッチング工程でEUVの優位性が示された。 [→続きを読む]